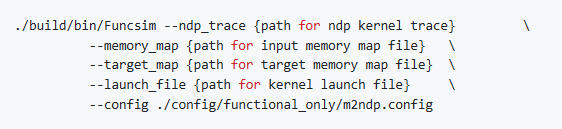

리뷰할 Simulator는 POSTECH PSAL에서 만든 M2NDP의 Cycle level simulator이다.https://github.com/PSAL-POSTECH/M2NDP-public?tab=readme-ov-file M2NDP가 뭔지 궁금한 사람들은 아래 논문 링크를 참고해 읽어보도록 하자.https://arxiv.org/abs/2404.19381 해당 논문에서 주장하는 low overhead GP NDP in CXL Memory를 실험하기 위해 직접 Simulator를 구현한 것이다. 해당 simulator의 특징은 크게 3가지이다. 1. NDP kernel operation이 정상적으로 이루어지는지 결과를 확인하는 FuncSim2. 정상적인 동작을 하는지 확인한 NDP Kernel을 cy..